# XMSS and Embedded Systems XMSS Hardware Accelerators for RISC-V

Wen Wang<sup>1</sup>, Bernhard Jungk<sup>2</sup>, Julian Wälde<sup>3</sup>, Shuwen Deng<sup>1</sup>, Naina Gupta<sup>4</sup>, Jakub Szefer<sup>1</sup>, and Ruben Niederhagen<sup>3</sup>

Yale University, New Haven, CT, USA {wen.wang.ww349, shuwen.deng, jakub.szefer}@yale.edu

<sup>2</sup> Independent Researcher

bernhard@projectstarfire.de

<sup>3</sup> Fraunhofer SIT, Darmstadt, Germany

ruben@polycephaly.org

<sup>4</sup> Fraunhofer Singapore, Singapore

naina.gupta@fraunhofer.sg

Abstract. We describe a software-hardware co-design for the hashbased post-quantum signature scheme XMSS on a RISC-V embedded processor. We provide software optimizations for the XMSS reference implementation for SHA-256 parameter sets and several hardware accelerators that allow to balance area usage and performance based on individual needs. By integrating our hardware accelerators into the RISC-V processor, the version with the best time-area product generates a key pair (that can be used to generate 2<sup>10</sup> signatures) in 3.44s, achieving an over 54× speedup in wall-clock time compared to the pure software version. For such a key pair, signature generation takes less than 10 ms and verification takes less than 6 ms, bringing speedups of over  $42\times$  and 17× respectively. We tested and measured the cycle count of our implementation on an Intel Cyclone V SoC FPGA. The integration of our XMSS accelerators into an embedded RISC-V processor shows that it is possible to use hash-based post-quantum signatures for a large variety of embedded applications.

**Keywords:** XMSS · hash-based signatures · post-quantum cryptography · hardware accelerator · FPGA · RISC-V

#### 1 Introduction

Due to the continued computerization and automation of our society, more and more systems from consumer products and Internet-of-Things (IoT) devices to cars, high-speed trains, and even nuclear power plants are controlled by embedded computers that often are connected to the Internet. Such devices can have a severe impact not only on our information security but increasingly also on our physical safety. Therefore, embedded devices must provide a high level of protection against cyber attacks — despite their typically restricted computing resources. If an attacker is able to disrupt the authenticity of transmitted data,

he or she can undermine the security of the system in many ways, e.g., malicious firmware can be loaded or contents of a digital document can be changed without being detected. Authenticity of the data is commonly ensured using digital signature schemes, often based on the DSA and ECDSA algorithms [22].

Such currently used asymmetric cryptographic algorithms, however, are vulnerable to attacks using quantum computers: Shor's algorithm [24,25] is able to factor integers and compute discrete logarithms in polynomial time and Grover's algorithm [10] provides a quadratic speedup for brute-force search. In light of recent advances in quantum-computer development and increased research interest in bringing practical quantum computers to life, a new field of post-quantum cryptography (PQC) has evolved [4], which provides cryptographic algorithms that are believed to be secure against attacks using quantum computers. This paper focuses on one of these algorithms, the eXtended Merkle Signature Scheme (XMSS), which has been standardized by the IETF [15].

XMSS is a stateful hash-based signature scheme proposed in 2011 by Buchmann, Dahmen and Hülsing [6]. It is based on the Merkle signature scheme [19] and proven to be a forward-secure post-quantum signature scheme with minimal security assumptions: Its security is solely based on the existence of a second pre-image resistant hash function family and a pseudorandom function (PRF) family. Both of these function families can be efficiently constructed even in the presence of large quantum computers [6]. Therefore, XMSS is considered to be a practical post-quantum signature scheme. Due to its minimal security assumptions and its well understood security properties, XMSS is regarded as one of the most confidence-inspiring post-quantum signature schemes.

Embedded devices will need to use algorithms such as XMSS to make them future-proof and to ensure their security even in the light of practical quantum computers. One of the increasingly popular processor architectures for embedded devices is the RISC-V architecture. It is an open and free architecture that is proving to be a practical alternative to close-source designs. Consequently, this work uses a RISC-V-based system on chip (SoC) (see Section 3) as a representative for embedded system architectures and shows how to efficiently deploy the post-quantum signature scheme XMSS on an embedded device, with the help of new hardware accelerators.

Hash-based signature schemes such as XMSS have relatively high resource requirements. They need to perform thousands of hash-computations for key generation, signing and verification and need sufficient memory for their relatively large signatures. Therefore, running such post-quantum secure signature schemes efficiently on a resource-constrained embedded system is a difficult task. This work introduces a number of hardware accelerators that provide a good time-area trade-off for implementing XMSS on RISC-V.

Our Contributions. Our work describes a software-hardware co-design of XMSS achieving 128 bit post-quantum security in an embedded systems setting To speed up the XMSS computations, we first provide SHA-256-specific software optimizations for the XMSS reference implementation. Based on the optimized XMSS software implementation, we then develop several hardware accelerators

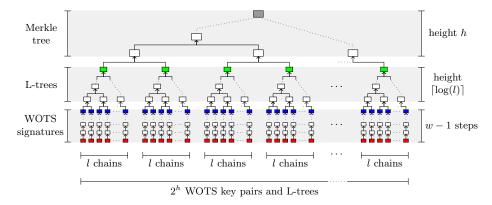

Fig. 1: XMSS tree with binary Merkle hash tree and WOTS instances with L-trees as leaves. Red nodes are the WOTS private key and blue nodes are the WOTS public key values. Green nodes are the L-tree roots and the gray node is the XMSS public key.

to speed up the most compute-intensive operations in XMSS. Our experimental results show a significant speedup of running XMSS on our software-hardware co-design compared to the pure (optimized) reference software version.

The source code for our work is publicly available under the open source GPLv3 license at https://caslab.csl.yale.edu/code/xmsshwswriscv/. An extended version of this work is available as Cryptology ePrint Archive, Report 2018/1225 [28].

#### 2 Preliminaries

In this section, we give an introduction to the relevant aspects of the XMSS signature scheme and briefly recapitulate the functionalities of SHA-256.

# 2.1 XMSS

XMSS [15] is a stateful digital signature scheme based on the Merkle signature scheme [19]. Similar to the Merkle signature scheme, XMSS uses a variant of the Winternitz one-time signature scheme (WOTS or Winternitz-OTS) to sign individual messages. One private/public WOTS key pair is used to sign one single message (with the private secret key) and to verify the signature (with the corresponding public verification key). To be able to sign up to  $2^h$  messages, XMSS uses  $2^h$  pairs of WOTS secret and verification keys. To reduce the size of the public key, a Merkle hash tree of height h and binary L-trees are used to reduce the authenticity of many WOTS verification keys to one XMSS public key. Since each WOTS key must only be used once, the signer needs to remember which WOTS keys already have been used. Hence, the scheme is stateful. Figure 1 shows the overall structure of XMSS.

The XMSS standard also defines multi-tree versions called XMSS^MT where the leaf nodes of a higher-level tree are used to sign the root of another tree. In this paper, we mainly consider single-tree XMSS. However, our results apply to multi-tree XMSS as well in a straightforward way. For a detailed description of XMSS and XMSS^MT please refer to IETF RFC 8391 [15] and to [6].

In the following we briefly introduce the XMSS address scheme, WOTS, the L-tree construction, and the procedure for constructing the Merkle tree. We also give an introduction to XMSS key generation, signing, and verification.

Address Scheme. XMSS uses a hash-function address scheme throughout the Merkle tree, L-tree, and WOTS computations to uniquely identify each individual step in the overall graph. These addresses are used to derive keys for keyed hash functions that are unique for each specific location in the graph. Each address is composed of eight 32 bit fields, with fields for, e.g., the level within a tree and the leaf index. In total, an XMSS address has a size of 256 bit. For more details about the hash function address scheme, please refer to IETF RFC 8391 [15, Sect. 2.5].

Winternitz OTS. The WOTS scheme was first mentioned in [19]. For signing a message digest D of n-byte length, WOTS uses a cryptographically secure hash function with n-byte output strings to compute hash chains. The message digest is interpreted as binary representation of an integer d. First, d is split into  $l_1 = \lceil 8n/\log_2(w) \rceil$  base-w words  $d_i, 0 \le i < l_1$  and a checksum  $c = \sum_{i=0}^{l_1} w - 1 - d_i$  is computed for these base-w words (w is called the "Winternitz parameter"). The checksum c is split into  $l_2 = \lfloor \log_2(l_1(w-1))/\log_2(w)) + 1 \rfloor$  base-w words  $c_i, 0 \le i < l_2$  as well. WOTS key generation, signing, and verification are performed as follows:

- − To create a private/public WOTS key pair, Alice computes  $l = l_1 + l_2$  secret strings  $s_{0,i}$  for  $0 \le i < l$ , each of n-byte length (for example using a secret seed and a PRF). These l n-byte strings are the private WOTS key. Then, Alice uses a chaining function to compute l hash chains of length w 1, hashing each  $s_{0,i}$  iteratively w 1 times. The resulting chain-head values  $s_{w-1,i}, 0 \le i < l$  of n-byte length are the public WOTS key of Alice.

- To sign a message digest, d is split into  $l_1$  base-w words together with  $l_2$  base-w checksum values computed as described above, Alice (re-)computes the intermediate chain values  $(s_{d_0,0},s_{d_1,1},\ldots,s_{d_{l_1-1},l_1-1},s_{c_0,0},s_{c_1,1},\ldots,s_{c_{l_2-1},l_2-1})$  starting from her private key values. These  $l=l_1+l_2$  values are the signature.

- When Bob wants to *verify* the signature, he recomputes the remaining chain steps by applying  $w 1 d_i$  hash-function iterations to signature value  $s_{d_i,0}$  and compares the results with the corresponding public key values. If all chain-head values match the public WOTS key, the signature is valid.

XMSS uses a modified WOTS scheme, sometimes referred to as WOTS+ or as W-OTS+ [13]; we use the term WOTS+ only when a explicit distinction from "original" WOTS is required for clarification. WOTS+ uses a function chain() as chaining function that is a bit more expensive than the simple hash-chain

function described above. The function chain() uses a keyed pseudo-random function  $\operatorname{prf}_k:\{0,1\}^{256}\mapsto\{0,1\}^{8n}$  and a keyed hash-function  $\operatorname{f}_{k'}:\{0,1\}^{8n}\mapsto\{0,1\}^{8n}$ . Within each chain step, the function chain() first computes a unique n-byte key k' and a unique n-byte mask using the  $\operatorname{prf}_k()$  function. The input to  $\operatorname{prf}_k()$  is the hash function address of the current step (including the chain step and a marker for the usage as key or as mask). The key k for  $\operatorname{prf}_k()$  is a seed that is part of the XMSS public key. The mask is then XOR-ed with the n-byte output from the previous chain-function call (or the initial WOTS+ chain n byte input string) and the result is used as input for the hash-function  $\operatorname{f}()$  under the key k', which gives the n-byte output of the chaining function chain() in the last iteration step.

The WOTS+ secret key consists of l (l is defined as described above for WOTS) pseudo-random strings of n-bytes in length. The XMSS specification does not demand a certain function to compute the WOTS+ private key. In the XMSS reference implementation, they are generated using the  $\operatorname{prf}_k()$  function with the local address (including the chain index) as input and keyed with the XMSS secret key seed. Each WOTS+ secret key maps to one corresponding WOTS+ public key, which is computed by calling the chaining function chain() with w-1 iteration steps. Signing and verification in WOTS+ work as described above for WOTS using the WOTS+ chaining function. The more complex structure of the chaining function of WOTS+ compared to WOTS is required for multi-target resistance and within the XMSS security proof.

**L-tree.** The leaf nodes of an XMSS tree are computed from the WOTS+ public keys by using an unbalanced binary tree of l leaf nodes (one leaf node for each WOTS+ public key value), hence called L-tree. The nodes on each level of the L-tree are computed by hashing together two nodes from the lower level. A tree hash function hash<sub>rand</sub>:  $\{0,1\}^{8n} \times \{0,1\}^{8n} \mapsto \{0,1\}^{8n}$  is used for this purpose.

The function hash<sub>rand</sub>() uses the keyed pseudo-random function  $\operatorname{prf}_k()$  and a keyed hash-function  $h_{k''}: \{0,1\}^{16n} \mapsto \{0,1\}^{8n}$ . First, an *n*-byte key k'' and two *n*-byte masks are computed using the  $\operatorname{prf}_k()$  with the address (including the L-tree level and node index) as input and the same public seed as used for WOTS+ as key. The masks are then each XOR-ed to the two *n*-byte input strings representing the two lower-level nodes and the results are concatenated and used as input for the hash-function h() keyed with k'', which gives the *n*-byte output of the tree hash function hash<sub>rand</sub>().

To be able to handle the pairwise hashing at levels with an odd number of nodes, the last node on these levels is lifted to a higher level until another single node is available. The root of the L-tree gives one single hash-value, combining the l WOTS+ public keys into one WOTS+ verification key.

XMSS Merkle Tree. In order to obtain a small public key, the authenticity of many WOTS verification keys (i.e., L-tree root keys) is reduced to one XMSS public key using a binary Merkle tree. Similar to the L-tree construction, on each level of the binary tree, neighbouring nodes are pairwise hashed together to obtain one single root node that constitutes the XMSS public key (see Figure 1).

**XMSS Key Generation.** XMSS key generation is quite expensive: In order to compute the XMSS public key, i.e., the root node of the Merkle tree, the entire XMSS tree needs to be computed. Depending on the height h of the tree, thousands to millions of hash-function calls need to be performed. XMSS key generation starts by generating  $2^h$  leaf nodes of the Merkle tree. Each leaf node consists of an WOTS instance together with an L-tree. For each WOTS instance, first l WOTS private keys are generated. These are then used to compute the l WOTS chains to obtain l WOTS public keys and then the L-trees on top of these. Once all  $2^h$  L-tree root nodes have been computed, the Merkle tree is computed to obtain the XMSS public key.

The XMSS public key consists of the n-byte Merkle tree root node and an n-byte public seed required by the verifier to compute masks and public hash-function keys using the function  $\operatorname{prf}_k()$  within the WOTS-chain, L-tree, and Merkle tree computations. The XMSS standard does not define a format for the XMSS private key. In the XMSS reference implementation that accompanies the standard, an n-byte secret seed is used to generate the WOTS secrets using a pseudo random function (e.g.,  $\operatorname{prf}_k()$ ).

**XMSS Signature Generation.** XMSS is a stateful signature scheme: Each WOTS private/public key pair must be used only once; otherwise, the scheme is not secure. To determine which WOTS key pair already has been used, an *n*-byte leaf index (the state) is stored with the private key. The index defines which WOTS key pair will be used for the next signature; after each signature generation, the index must be increased.

Similar to most signature schemes, for signing an arbitrary-length message or a document M, first a message digest of M is computed; details can be found in [15, Sect. 4.1.9]. The digest M' is then signed using the selected WOTS instance. This results in l n-byte values corresponding to the base-w decomposition of M' including the corresponding checksum. Furthermore, in order to enable the verifier to recompute the XMSS public root key from a leaf node of the Merkle tree, the signer needs to provide the verification path in the Merkle tree, i.e., h n-byte nodes that are required for the pairwise hashing in the binary Merkle tree, one node for each level in the Merkle tree.

Therefore, in the worst case, the signer needs to recompute the entire XMSS tree in order to select the required nodes for the verification path. There are several optimization strategies using time-memory trade-offs to speed up signature generation. The BDS tree traversal algorithm [7] targets at reducing the worst case runtime of signature generation by computing a certain amount of nodes in the Merkle tree at each signature computation and storing them alongside the XMSS state.

XMSS Signature Verification. Compared to key generation, XMSS signature verification is fairly inexpensive: An XMSS public key contains the Merkle root node and the public seed. An XMSS signature contains the WOTS leaf index, l WOTS-signature chain values, and the verification path consisting of h Merkletree pair values, one for each level in the tree. The verifier computes the message

digest M' and then recomputes the WOTS verification key by completing the WOTS chains and computing the L-tree. The verifier then uses the Merkle-tree pair values to compute the path through the Merkle tree and finally compares the Merkle tree root node that was obtained with the root node of the sender's public key. If the values are equal, verification succeeds and the signature is sound; otherwise verification fails and the signature is rejected.

**Parameter Set.** RFC 8391 defines parameter sets for the hash functions SHA-2 and SHAKE targeting classical security levels of 256 bit with n=32 and 512 bit with n=64 in order to provide 128 bit and 256 bit of security respectively against attackers in possession of a quantum computer [15, Sect. 5]. The *required* parameter sets, as specified in [15, Sect. 5.2], all use SHA-256 to instantiate the hash functions (SHA-512 and SHAKE are optional). Therefore, for this work, we focus on the SHA-256 parameter sets with n=32.

For SHA-256, three different parameter sets are provided in RFC 8391 [15, Sect. 5.3], all with n=32 and w=16 but with h=10, h=16, or h=20. In general, a bigger tree height h leads to an exponential growth in the run time of key generation. For verification the run time is only linearly impacted. The naive approach for signing requires one to recompute the entire tree and thus is as expensive as key generation. However, by use of the BDS tree traversal algorithm [7], the tree height has only a modest impact on the run time. Multitree versions of XMSS can be used to speed up the computations at the cost of larger signature sizes (e.g., to improve key generation and signing performance or to achieve a larger h). We are using h=10 throughout our experiments; however, our implementation is not restricted to this value.

#### 2.2 SHA-256

The hash function SHA-256 [21] computes a 256 bit hash value from a variable-length input. SHA-256 uses a 256 bit internal state that is updated with 512 bit blocks of the input. SHA-256 defines a padding scheme for extending variable-length inputs to a multiple of 512 bit. SHA-256 works as follows:

- 1. Initialize the internal state with a well-defined IV (see [21, Sect. 4.2.2]).

- 2. Extend the  $\ell$ -bit input message with a padding to make the length of the padded input a multiple of 512 bit:

- append a single 1 bit to the input message, then

- append  $0 \le k$  0 bit such that  $\ell+1+k+64$  is minimized and is a multiple of 512, and finally

- append  $\ell$  as a 64 bit big-endian integer.

- 3. Iteratively apply a compression function to all 512 bit blocks of the padded input and the current internal state to obtain the next updated internal state.

- 4. Once all 512 bit blocks have been processed, output the current internal state as the hash value.

The compression function uses the current internal state and a  $512\,\mathrm{bit}$  input block and outputs an updated internal state. For SHA-256, the compression function is composed of  $64\,\mathrm{rounds}$ .

#### 3 RISC-V

Software-hardware co-design has been adopted as a common discipline for designing embedded system architectures since the 1990s [27]. By combining both software and hardware in an embedded system, a trade-off between software flexibility and hardware performance can be achieved depending on the user's needs. To accelerate XMSS computations, we developed a software-hardware co-design of XMSS by moving the most compute-intensive operations to hardware while keeping the rest of the operations running in software. Our software-hardware co-design of XMSS is developed based on a RISC-V platform.

RISC-V. The RISC-V instruction set architecture (ISA) is a free and open architecture, overseen by the RISC-V Foundation with more than 100 member organizations<sup>5</sup>. The RISC-V ISA has been designed based on well-established reduced instruction set computing (RISC) principles. It has a modular design, consisting of base sets of instructions with optional instruction set extensions. Due to its modular design, the RISC-V ISA is an increasingly popular architecture for embedded systems. It is used, e.g., as a control processor in GPUs and in storage devices [11], for secure boot and as USB security dongle [20], and for building trusted execution environments (TEE) with secure hardware enclaves<sup>6</sup>. Since the RISC-V ISA is an open standard, researchers and industry can easily extend and adopt it in their designs without IP constraints.

VexRiscv. First-prize winner in the RISC-V Soft-Core CPU Contest of 2018<sup>7</sup>, VexRiscv<sup>8</sup> is a 32-bit RISC-V CPU implementation written in SpinalHDL<sup>9</sup>, which is a Scala-based high-level hardware description language. It supports the RV32IM instruction set and implements a five-stage in-order pipeline. The design of VexRiscv is very modular: All complementary and optional components are implemented as plugins and therefore can easily be integrated and adapted into specific processor setups as needed. The VexRiscv ecosystem provides memories, caches, IO peripherals, and buses, which can be optionally chosen and combined as required.

Murax SoC. The VexRiscv ecosystem also provides a complete predefined processor setup called "Murax SoC" that has a compact and simple design and aims at small resource usage. The Murax SoC integrates the VexRiscv CPU

<sup>&</sup>lt;sup>5</sup> https://riscv.org/

<sup>6</sup> https://keystone-enclave.org/

<sup>7</sup> https://riscv.org/2018/10/risc-v-contest/

<sup>8</sup> https://github.com/SpinalHDL/VexRiscv/

<sup>9</sup> https://spinalhdl.github.io/SpinalDoc/

with a shared on-chip instruction and data memory, an Advanced Peripheral Bus (APB), a JTAG programming interface, and a UART interface. It has very low resource requirements (e.g., only 1350 ALMs on a Cyclone V FPGA) and can operate on its own without any further external components.

The performance of the Murax SoC is comparable to an ARM Cortex-M3: A multi-tree version of XMSS has been implemented on an embedded ARM Cortex-M3 platform in [16] (see also Section 7). We compiled a pure C-version of the code from [16] for both an ARM Cortex-M3 processor and the Murax SoC and compared their performance (see the bottom lines of Table 7). In terms of cycle count, the Cortex-M3 is only about  $1.5\times$  faster than the Murax SoC. Therefore, we conclude that the Murax SoC is a good representative for an embedded system processor with low resources. As opposed to an ARM Cortex-M3 platform, however, the Murax SoC is fully free, open, and customizable and thus is an ideal platform for our work.

Extending the Murax SoC with new hardware accelerators can be implemented easily in a modular way using the APB bus. We used this feature for our XMSS accelerators. Depending on different use cases, our open-source software-hardware co-design of XMSS can be migrated to other RISC-V or embedded architectures with small changes to the interface.

**Setup.** We evaluated our design using a DE1-SoC evaluation board from Terasic as test-platform. This board has an Intel (formerly Altera) Cyclone V SoC 5CSEMA5F31C6 device. We used Intel Quartus Software Version 16.1 (Standard Edition) for synthesis. On the DE1-SoC, we are running the Murax SoC described above with additional accelerators that will be described in Section 5. The DE1-SoC board is connected to a host computer by a USB-JTAG connection for programming the FPGA, a USB-serial connection for IO of the Murax SoC, and a second USB-JTAG connection for programming and debugging the software on the Murax SoC.

We configured the on-chip RAM size of the Murax SoC to 128 kB, which is sufficient for all our experiments. We tested our implementations on the DE1-SoC board at its default clock frequency of 50 MHz; however, to achieve a fair comparison, our speedup reports presented in the following sections are based on the maximum frequency reported by the synthesis tool. Our implementation is neither platform-specific nor dependent on a specific FPGA vendor.

# 4 Software Implementation and Optimization

We used the official XMSS reference implementation<sup>10</sup> with the BDS algorithm [7] for tree traversal as software-basis for this work. We applied minor modifications to the XMSS reference code to link against the mbed TLS library<sup>11</sup> instead of OpenSSL, because mbed TLS generally is more suitable for

$<sup>^{10}</sup>$  https://github.com/joostrijneveld/xmss-reference/,  $commit\ 06281e057d9f5d$

<sup>11</sup> https://tls.mbed.org/

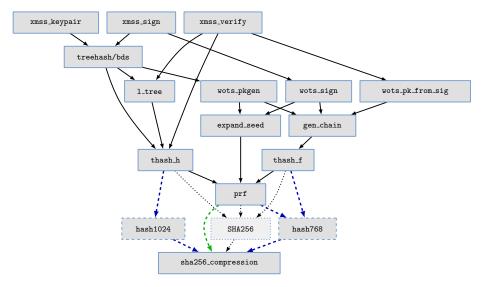

Fig. 2: Simplified XMSS call graph. Function calls that have been removed during software optimization are displayed with dotted nodes and arrows, added calls are dashed. The "fixed input length" optimization is marked in blue, the "pre-computation" optimization is marked in green.

resource-restricted embedded platforms such as the Murax SoC platform and its SHA-256 implementation has less library-internal dependencies than that of OpenSSL, which simplifies stand-alone usage of SHA-256.

To have a fair reference point for the comparison of a pure software implementation with our hardware accelerators, we implemented two software optimizations for the XMSS reference software implementation as described in the following paragraphs. These optimizations are also helpful on other processor architectures but only work for SHA-256 parameter sets, because they depend on the specific SHA-256 block size and padding scheme. We are going to provide our software optimizations to the maintainers of the XMSS reference implementation so they can integrate them if they wish to.

Figure 2 shows a simplified XMSS call graph for both the original source code version and the changes that we applied for optimizations as described below.

Fixed Input Length. In the XMSS software reference implementation, around 90% of the time is spent inside the hash-function calls. Therefore, the SHA-256 function is most promising for optimization efforts. In particular for short-length inputs, a significant overhead is caused by computing the SHA-256 padding. However, within the XMSS scheme, the inputs of almost all SHA-256 calls have a well-known, fixed length: A general, arbitrary-length SHA-256 computation is only required when computing the actual hash digest of the input message, which is called only once for signing and once for verifying. For all the other SHA-256 calls, the length of the input data is either 768 bit or 1024 bit depending on

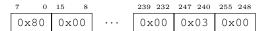

#### 256-bit hash768-padding:

#### 512-bit hash1024-padding:

| 7  | 0   | 15 8 | $239 \ 232$ | 247 240 | 255 248 | $263\ 256$ | $495 \ 448$ | 503 496 | $511 \ 504$ |

|----|-----|------|-------------|---------|---------|------------|-------------|---------|-------------|

| 0: | x80 | 0x00 | <br>0x00    | 0x00    | 0x00    | 0x00       | <br>0x00    | 0x04    | 0x00        |

Fig. 3: Fixed padding for hash768 and hash1024

.

where SHA-256 is called within the XMSS scheme: An input length of 768 bit is required within the PRF and within the WOTS-chain computation; an input length of 1024 bit is required within the Merkle tree and the L-trees to hash two nodes together. Therefore, we can eliminate the overhead for the padding computation of the SHA-256 function by "hardcoding" the two required message paddings, given that their lengths are known beforehand.

We implemented two specialized SHA-256 functions: The function hash768 targeting messages with a fixed length of 768 bit and hash1024 targeting messages with fixed length of 1024 bit. Figure 3 shows the padding for hash768 and hash1024. Since SHA-256 has a block size of 512 bit, two blocks are required to hash a message of length 768 bit. Therefore, we need to hardcode a 256 bit padding for hash768 to fill up the second block to 512 bit. When a 768 bit message is fed to the hash768 function, the 256 bit padding is appended to the message. Then, the new 1024 bit padded message is divided into two 512 bit blocks and the compression function is performed on each of them one by one. Once the compression function on the second message block has finished, the internal state is read out and returned as the output. The SHA-256 standard always demands to append a padding even if the input length is a multiple of 512 bit. Therefore, for the hash1024 function a 512 bit padding is hardcoded similarly to hash768 and three calls to the compression function are performed.

Table 1 shows a comparison of the original XMSS reference implementation with an optimized version making use of the "fixed input length" optimization on the Murax SoC with parameters n=32, w=16 and h=10. The speedup for 768 bit inputs is about  $1.07\times$  and for 1024 bit inputs is about  $1.04\times$ . The use of 768 bit inputs is more common during the XMSS computations. Therefore, we see an about  $1.06\times$  speedup for WOTS computations as well as the key generation, signing, and verification operations in XMSS.

**Pre-Computation.** Pre-computation is commonly referred to as the act of performing an initial computation before runtime to generate a lookup table to avoid repeated computations during runtime. This technique is useful in improving real-time performance of algorithms at the expense of extra memory and extra preparatory computations [3]. In XMSS, a variant of this idea can be applied to improve the performance of the hash functions. Within XMSS, SHA-256

|                | 0                                                          | + "fixed inp         | 0            | -                    | -    | computation" |  |

|----------------|------------------------------------------------------------|----------------------|--------------|----------------------|------|--------------|--|

|                | $\begin{array}{c} \text{Cycles} \\ \text{(A)} \end{array}$ | Cycle (B)            | Speedup (AB) | Cycles<br>(C)        | (BC) | Speedup (AC) |  |

| hash768        | $11.5 \times 10^3$                                         | $10.7 \times 10^{3}$ | 1.07         | $5.87 \times 10^{3}$ | , ,  | 1.95         |  |

| hash1024       | $16.2 \times 10^{3}$                                       | $15.6 \times 10^3$   | 1.04         | _                    | _    | _            |  |

| WOTS-chain     |                                                            |                      | 1.08         | $371 \times 10^{3}$  | 1.43 | 1.54         |  |

| XMSS-leaf      | $42.2 \times 10^6$                                         | $39.8 \times 10^{6}$ | 1.06         | $27.7 \times 10^6$   | 1.44 | 1.53         |  |

| key generation |                                                            | $40.8 \times 10^{9}$ | 1.06         | $28.3 \times 10^{9}$ | 1.44 | 1.53         |  |

| signing        |                                                            | $55.0 \times 10^{6}$ | 1.06         | $38.4 \times 10^{6}$ |      | 1.52         |  |

| verification   | $26.7 \times 10^{6}$                                       | $25.2 \times 10^{6}$ | 1.06         | $17.4 \times 10^{6}$ | 1.45 | 1.54         |  |

**Table 1:** Cycle count and speedup of the "fixed input length" optimization and for both, the "fixed input length" and the "pre-computation" optimizations, on the Murax SoC with parameters n=32, w=16 and h=10.

is used to implement four different keyed hash-functions, the function thash\_f for computing f() in the WOTS-chains, the function thash\_h for h() in the tree hashing, and the function prf for computing the prf(), generating masks and hash-function keys. Furthermore, SHA-256 is used to compute the message digest that is signed using a WOTS private key. The domain separation and the keying for these four functions are achieved by computing the input to SHA-256 as the concatenation of a 256 bit domain separator value (distinct for these four functions), the 256 bit hash key, and the hash-function input. Since SHA-256 operates on 512 bit blocks, one entire block is required for domain separation and keying of the respective hash function.

In case of the prf, for all public-key operations when generating masks and hash-function keys for the WOTS chain, the L-tree and Merkle tree operations, the key to the prf is the 256 bit XMSS public seed. Thus, both the 256 bit domain separator and the 256 bit hash-function key are the same for all these calls for a given XMSS key pair. These two parts fit exactly into one 512 bit SHA-256 block. Therefore, the internal SHA-256 state after processing the first 512 bit block is the same for all these calls to the prf and based on this fact, we can save one SHA-256 compression function call per prf-call by pre-computing and replaying this internal state. The internal state can either be computed once and stored together with the XMSS key or each time an XMSS operation (key generation, signing, verification) is performed. This saves the computation on one of the two input blocks in hash768 used in the prf. For hash1024, this optimization is not applicable since the fixed input block pattern does not exist.

At the first call to prf, we store the SHA-256 context of mbed TLS for later usage after the first compression function computation. The state includes the internal state and further information such as the length of the already processed data. When the prf is called during XMSS operations, we first create a copy of the initially stored prf SHA-256 context and then perform the following prf()

operations based on this state copy, skipping the first input block. The cost for the compression function call on the first SHA-256 block within the prf is therefore reduced to a simple and inexpensive memory-copy operation.

Performance measurements and speedup for our pre-computation optimization are shown in Table 1. For hash768 we achieve a  $1.83\times$  speedup over the "fixed input length" optimization, because only one SHA-256 block needs to be processed instead of two. For WOTS-chain computations we obtain a  $1.43\times$  speedup and for the overall XMSS leaf computations an about  $1.44\times$  speedup. The expected speedup for Merkle tree computations is about the same as for the L-tree computations since the trees are constructed in a similar way. Table 1 shows that we achieve an overall speedup of more than  $1.5\times$  including both optimizations also for the complete XMSS operations, i.e., key generation, signing, and verification. We observed a similar speedup on an Intel i5 CPU. Similar speedups can be achieved on other architectures as well, e.g., ARM processors.

## 5 Hardware Acceleration

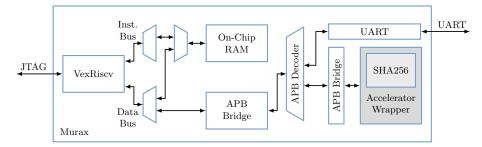

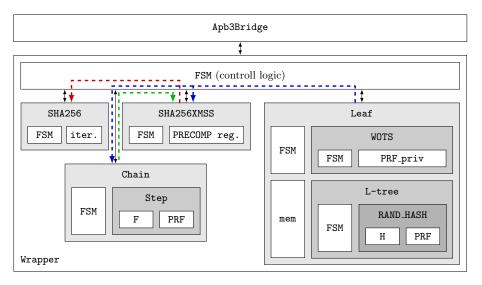

To further accelerate the XMSS computations, we developed several dedicated hardware modules together with software interfaces for the XMSS software. As shown in Figure 4, the Murax SoC uses an APB for connecting peripherals to the main CPU core. The peripheral can be accessed by the software running on the Murax SoC via control and data registers that are mapped into the address space. Therefore, the software interface can simply use read and write instructions to communicate with a hardware module. Due to the modularity of the VexRiscv implementation, dedicated hardware modules can be easily added to and removed from the APB before synthesis of the SoC (see Section 3).

The hardware accelerators are connected to the APB using a bridge module: The Apb3Bridge module connects on one side to the 32 bit data bus and the control signals of the APB and on the other side to the hardware accelerator. It provides a 32 bit control register, which is mapped to the control and state ports of the hardware accelerator, and data registers for buffering the input data, which are directly connected to the input ports of the hardware accelerator. The control and data registers are mapped to the APB as 32 bit words using a multiplexer, selected by the APB address port on APB write; the control register and the output ports of the hardware accelerator are connected in the same way to be accessed on APB read. This allows the software to communicate with the accelerators via memory-mapped IO using simple load and store instructions.

We modified the corresponding software functions in the optimized XMSS implementation to replace them with function calls to our hardware accelerators as follows: The function first sets control bits (e.g., RESET, INIT) to high in the control register. When these bits are received as high by the Apb3Bridge module, it raises the corresponding input signals of the hardware accelerator. Similarly, the input data is sent to the corresponding hardware accelerator via the APB bus in words of width 32 bit. Then the hardware accelerator is triggered using the control register, performs its computation, and raises a done signal when it

**Fig. 4:** Schematic of the Murax SoC. Hardware accelerators are connected to the APB. Details on the hardware accelerators are shown in Figure 5.

finishes. Once the software is ready to read the result, it keeps polling the control register until the DONE bit is set high. The software then can read the results via the APB in words of 32 bit.

#### 5.1 General-Purpose SHA-256 Accelerator

The first hardware module we developed is the SHA256 module, which is a general-purpose hash accelerator that accepts variable length inputs. The SHA256 module is used as the building block in the XMSS-specific hardware accelerators described in the following sub-sections. It has a similar interface as the generic SHA-256 compression function in software: It receives a 512 bit data block as input and computes the compression function, updating an internal 256 bit state. This state can be read out as the 256 bit digest when the SHA-256 computation is finished. Padding is performed in software as before.

We developed the module SHA256 by implementing an iterative version of SHA-256 by computing one round of SHA-256 in one clock cycle. Therefore, we require 64 clock cycles to process one SHA-256 data block. This provides a good trade-off between throughput and area consumption similar to [12]. The SHA256 module is a generic hash core without platform-specific optimizations that runs on any FPGA platform. Users can easily use a platform-optimized SHA-256 core within our hardware modules, e.g., [8,17,23].

Hardware Support for Software Optimizations. The software optimization of SHA-256 exploiting fixed input lengths of the SHA-256 function described in Section 4 can be mapped in a straightforward way to the SHA256 module. The software prepares the SHA-256 input chunks with pre-defined paddings just as before and then transfers each chunk to the SHA256 module for processing. Therefore, the speedup achieved for the pure software version can also be exploited for this hardware accelerator.

In order to support the "pre-computation" optimization, (Section 4), we added an interface to the SHA256 module that allows to set the internal state of the SHA256 module from software. Reading the internal state is the same as reading the SHA-256 message digest at the end of the hash computation.

| Design   | Cycles                                           | Area (ALM) | _      | Fmax<br>(MHz) | Time (µs) | $Time \times Area$ (relative) | Speedup |  |  |  |  |

|----------|--------------------------------------------------|------------|--------|---------------|-----------|-------------------------------|---------|--|--|--|--|

|          |                                                  |            | one 5  | 512 bit b     | lock      |                               |         |  |  |  |  |

| SHA256   | 64                                               | 1180       | 1550   | 100           | 0.639     | _                             | _       |  |  |  |  |

| h        | hash768 with pre-computation (one 512 bit block) |            |        |               |           |                               |         |  |  |  |  |

| Murax    | 4950                                             | 1350       | 1660   | 152           | 32.6      | 9.22                          | 1.00    |  |  |  |  |

| + SHA256 | 253                                              | 2860       | 3880   | 99.9          | 2.53      | 1.00                          | 12.9    |  |  |  |  |

| has      | h768 w                                           | ithout     | pre-co | mputat        | ion (two  | 512 bit bloo                  | ks)     |  |  |  |  |

| Murax    | 10,700                                           | 1350       | 1660   | 152           | 70.4      | 8.76                          | 1.00    |  |  |  |  |

| + SHA256 | 576                                              | 2860       | 3880   | 99.9          | 5.77      | 1.00                          | 12.2    |  |  |  |  |

|          | hash1024 (three 512 bit blocks)                  |            |        |               |           |                               |         |  |  |  |  |

| Murax    | 15,600                                           | 1350       | 1660   | 152           | 102       | 10.5                          | 1.00    |  |  |  |  |

| + SHA256 | 700                                              | 2860       | 3880   | 99.9          | 7.01      | 1.00                          | 14.6    |  |  |  |  |

**Table 2:** Performance of the hardware module SHA256 and comparisons of performing the SHA-256 compression function on different numbers of 512 bit blocks when called from the RISC-V software on a Murax SoC and on a Murax SoC with a SHA256 accelerator (all using the "fixed input length" optimization in software, i.e., cost for SHA-256 padding is not included).

While the hardware is performing the hash computation, the software can go on transferring the next data block to the SHA256 module. This reduces the communication overhead and increases the efficiency of the SHA256 module.

**Evaluation.** Table 2 shows performance, resource requirements, and maximum frequency of the SHA256 module. The module requires 64 cycles (one cycle per round) for computing the compression function on one 512 bit input block.

Table 2 also shows a comparison of computing one SHA-256 compression function call in software (design Murax) with calling the hardware module from the software (design "Murax + SHA256"). Transferring data to the SHA256 accelerator module and reading back the results contribute a significant overhead: The entire computation on a 512 bit input block (without SHA-256 padding computation) requires 253 cycles. This overhead is due to the simple bus structure of the Murax SoC; a more sophisticated bus (e.g., an AXI bus) may have a lower overhead — at a higher cost of resources. However, we achieve an almost 13× speedup over the software implementation of the SHA-256 compression function.

Table 6 shows the performance impact of the SHA256 module on XMSS computations (designs Murax and "Murax + SHA256", including both "fixed input length" and "pre-computation" software optimizations). For the key generation, signing and verification operations, the SHA256 module accounts for an about  $3.8 \times$  speedup in the XMSS scheme.

To further accelerate the XMSS computations in an efficient way, in the following we describe the XMSS-specific hardware accelerators that we developed. We first describe an XMSS-specific SHA-256 accelerator, which performs fixed-length SHA-256 padding and provides optional internal storage for one pre-computed state in hardware. Then, we describe how we use this XMSS-specific SHA-256 accelerator as building-block for larger hardware accelerators: An accelerator for WOTS-chain computations and an accelerator for XMSS-leaf generation including WOTS and L-tree computations.

## 5.2 XMSS-Specific SHA-256 Accelerator

In Section 4, we proposed two software optimizations for the XMSS scheme: "fixed input length" for accelerating SHA-256 computations on 768 bit and 1024 bit inputs and "pre-computation" for acceleration of the function prf(). For hardware acceleration, we introduced a general-purpose SHA-256 hardware module in Section 5.1, which replaces the SHA-256 compression function and thus naturally supports the "fixed input length" optimization and the "precomputation" optimization of the software implementation. However, both of the optimizations require to repeatedly transfer the same data, i.e., padding or the pre-computed state, to the SHA256 module. To eliminate this overhead and as building block for the hardware accelerator modules described in the following sub-sections, we developed an XMSS-specific SHA-256 accelerator, the SHA256XMSS module. It has a similar functionality as the general SHA256 module: however, the SHA256XMSS module supports both of the software optimizations internally: It only accepts complete input data blocks of size 768 bit or 1024 bit and adds the SHA-256 padding in hardware. In addition, it provides an optional internal 256 bit register for storing and replaying a pre-computed state.

Implementation. We used the SHA256 module as building block for the implementation of the SHA256XMSS module. All the SHA-256 compression computations in SHA256XMSS are done by interacting with the SHA256 module. In order to handle larger input blocks, the data\_in port of the SHA256XMSS module is 1024 bit wide. The SHA256XMSS module has an additional state machine to autonomously perform two or three compression-function iterations (depending on the input length). The state machine also takes care of appending the pre-computed SHA-256 padding to the input data before the last compression function computation. To select between different input lengths, the SHA256XMSS module has a message\_length input signal (low for 768 bit, high for 1024 bit). To support the "pre-computation" optimization, the SHA256XMSS module has a similar interface as described for the SHA256 module in Section 5.1, which allows to set the internal state from software.

To further support the pre-computation functionality in hardware, a 256 bit register can optionally be activated at synthesis time to the SHA256XMSS module for storing the fixed internal state. An input signal store\_intermediate is added for requesting to store the result of the first compression-function iteration in the internal 256 bit register. An input signal continue\_intermediate is

| Design               | Cycles             | Area<br>(ALM) | Reg. | Fmax<br>(MHz) | Time (µs) | $Time \times Area$ (relative) | Speedup |  |  |  |  |

|----------------------|--------------------|---------------|------|---------------|-----------|-------------------------------|---------|--|--|--|--|

|                      | two 512 bit blocks |               |      |               |           |                               |         |  |  |  |  |

| SHA256XMSS           | 128                | 1680          | 2070 | 89.7          | 1.43      | 1.77                          | 1.00    |  |  |  |  |

| + PRECOMP            | 64                 | 1900          | 2320 | 98.3          | 0.651     | 1.00                          | 2.19    |  |  |  |  |

| three 512 bit blocks |                    |               |      |               |           |                               |         |  |  |  |  |

| SHA256XMSS           | 192                | 1680          | 2070 | 89.7          | 2.14      | _                             | _       |  |  |  |  |

|                      |                    |               | has  | h768          |           |                               |         |  |  |  |  |

| Murax                | 10,700             | 1350          | 1660 | 152           | 70.4      | 16.0                          | 1.00    |  |  |  |  |

| + SHA256XMSS         | 274                | 3490          | 4890 | 97.8          | 2.80      | 1.06                          | 25.1    |  |  |  |  |

| + PRECOMP            | 247                | 3660          | 5170 | 97.6          | 2.53      | 1.00                          | 27.8    |  |  |  |  |

| hash1024             |                    |               |      |               |           |                               |         |  |  |  |  |

| Murax                | 15,600             | 1350          | 1660 | 152           | 102       | 13.1                          | 1.00    |  |  |  |  |

| + SHA256XMSS         | 458                | 3490          | 4890 | 97.8          | 4.68      | 1.00                          | 21.9    |  |  |  |  |

Table 3: Performance of hardware module SHA256XMSS and performance comparisons of SHA-256 computations for 768 bit and 1024 bit (functions hash768 and hash1024) when called from the RISC-V software on a Murax SoC and on a Murax SoC with a SHA256XMSS accelerator.

added for requesting to use the previously stored internal state instead of the first compression iteration. The pre-computation functionality can be enabled (marked as "+ PRECOMP" in the tables) or disabled at synthesis time in order to save hardware resources for a time-area trade-off.

To reduce the latency of data transfer between the SHA256XMSS module and the software, the SHA256XMSS module starts computation once the first input data block (512 bit) is received. While the SHA256XMSS module is operating on the first input block, the software sends the rest of the input data.

When the SHA256XMSS module is added to the Murax SoC as a hardware accelerator, it provides a SHA256 accelerator as well since the SHA256 module is used as its building block. To achieve this, a hardware wrapper is designed (as shown in Figure 5) which includes both the SHA256XMSS module and the SHA256 module. Apart from the control signals and input data, the bridge module Apb3Bridge also takes care of forwarding a 3 bit cmd signal from the software to the hardware wrapper. Depending on the value of cmd, the hardware wrapper further dispatches the signals to the corresponding hardware module (SHA256XMSS or SHA256) and triggers the computation. Similarly, based on the cmd value, the output data from the corresponding module is returned. The design of the hardware wrapper brings the flexibility that the SHA256XMSS module can not only accelerate XMSS-specific SHA-256 function calls, but also general SHA-256 function calls that accept variable length inputs, which may be helpful for some other applications running in the system.

Evaluation. Table 3 shows the performance, resource requirements, and maximum frequency of the SHA256XMSS module. When the pre-computation functionality is not enabled, it requires 128 cycles and 192 cycles respectively (one cycle per round) for computing the hash digests for input messages of size 768 bit and 1024 bit. When the pre-computation functionality of the SHA256XMSS module is enabled, the cycle count for computing the hash digests for input messages of size 768 bit is halved, because only one 512 bit block needs to be compressed instead of two. However, storing the pre-computed state to achieve this speedup increases ALM and register requirements. When the pre-computation functionality of the SHA256XMSS module is enabled, one hash768 call within design "Murax + SHA256XMSS + PRECOMP" obtains a speedup of around 27.8× over the plain Murax design.

Table 6 shows the performance impact of the SHA256XMSS module on XMSS key generation, signing, and verification (design Murax compared to "Murax + SHA256XMSS" and "Murax + SHA256XMSS + PRECOMP"). For these operations, the SHA256XMSS module accounts for an about  $5.4\times$  speedup with pre-computation enabled. Compared to adding a SHA256 module to the Murax SoC, this gives an over  $1.4\times$  speedup in accelerating XMSS computations.

#### 5.3 WOTS-chain Accelerator

The SHA256XMSS module provides a significant speedup to the XMSS computations. However, since inputs and outputs need to be written to and read from the SHA256XMSS module frequently, the raw speedup of the SHA-256 accelerator cannot fully be exploited: It actually takes more time to send the inputs to and to read the results from the accelerator than the accelerator requires for the SHA-256 operations. This overhead can significantly be reduced by performing several SHA-256 operations consecutively in hardware. In this case, the hardware accelerator needs to be able to prepare some of the inputs by itself.

The WOTS chain computations are an ideal candidate for such an optimization, because the prf() computations performed in each chain step share a large amount of their inputs (only a few bytes are modified in the address fields for each prf() computation) and the f() computations use previous hash-function outputs. Therefore, we implemented the hardware module Chain as dedicated hardware accelerator for the WOTS chain computations to accelerate the work of the software function gen\_chain (see Figure 2).

Implementation. One building block of the Chain module is the Step module, which implements the prf() and the keyed hash-function f() in hardware. The Step module takes in a 256 bit XMSS public seed, a 256 bit data string and a 256 bit address string as input and returns a 256 bit output. Within Step, two prf() computations and one f() computation are carried out in sequence using the hardware modules PRF and F. PRF and F are both implemented by interfacing with a SHA256XMSS module described in Section 5.2. The result generated by the first prf() computation is buffered in a 256 bit register and used later as hash-function key. Similarly the second prf() computation result is buffered in a 256 bit

| Design                       | Cycles                    | Area (ALM)           | Reg.                 | Fmax<br>(MHz)       |      | Time×Area<br>(relative) | Speedup              |

|------------------------------|---------------------------|----------------------|----------------------|---------------------|------|-------------------------|----------------------|

| Chain<br>+ PRECOMP           | 5960<br>4100              | 1940<br>2170         | 3060<br>3320         | 91.0<br>96.0        | 00.0 |                         | 1.00<br>1.53         |

| Murax<br>+ Chain<br>+ PRECOM | 530,000<br>6910<br>P 4990 | 1350<br>4350<br>4560 | 1660<br>6220<br>6460 | 152<br>91.6<br>95.2 |      | 1.02                    | 1.00<br>46.2<br>66.5 |

**Table 4:** Performance of the hardware module Chain and performance comparisons of calling the gen\_chain function from the RISC-V software on a Murax SoC and on a Murax SoC with a Chain accelerator, with parameters n=32 and w=16.

register MASK. The 256 bit input data then gets XOR-ed with MASK and sent to the final f() computation together with the previously computed hash key. The result of the f() computation is returned as the output of the Step module.

The hardware module Chain repeatedly uses the Step module. It has two input ports chain\_start and chain\_end, defining the start and end step for the WOTS chain computation respectively, e.g., 0 and w-1 when used in WOTS key generation. Each step in the Chain module uses its step index as its input address and the output from the previous step as its input data. The result from the last step is returned as the result of the Chain module. The "pre-computation" optimization (see Section 4) can be optionally enabled for the SHA256XMSS module before synthesis. To enable the optimization, the store\_intermediate port of the SHA256XMSS module is set to high for the very first prf() computation to request the SHA256XMSS module to store the result of the first compression-function in its internal 256 bit register. For all the following prf() computations, the input port continue\_intermediate of the SHA256XMSS module is raised high to request the usage of the previously stored internal state.

When the Chain module is added to the Murax SoC as a hardware accelerator, it provides a SHA256XMSS and a SHA256 accelerator as well since these modules are used as building blocks in Chain. A similar hardware wrapper as described for the SHA256XMSS accelerator in Section 5.2 is used.

**Evaluation.** Table 4 shows performance, resource requirements, and maximum frequency of the Chain module. Enabling the "pre-computation" optimization ("+ PRECOMP") results in a  $1.53\times$  speedup for the chain computations.

A comparison between the pure software and the software/hardware performance of the function gen\_chain is also provided in Table 4. When gen\_chain is called in the design "Murax + Chain + PRECOMP", a speedup of around  $66.5 \times$  is achieved compared to the pure software implementation using the Murax design.

Table 6 shows the performance impact of the Chain module on XMSS key generation, signing, and verification (Murax compared to "Murax + Chain" and "Murax + Chain + PRECOMP"). Note that since the Chain accelerator provides a SHA256XMSS accelerator as well, when a Chain module is added to the Mu-

rax SoC, apart from the function gen\_chain, the hash768 and hash1024 functions are also accelerated. The acceleration of the Chain module leads to a 23.9× speedup for both key generation and signing and a 17.5× speedup for verification when the pre-computation functionality is enabled. These speedups achieved are much higher compared to those achieved in the design with a SHA256XMSS/SHA256 accelerator, as shown in Table 6.

#### 5.4 XMSS-leaf Generation Accelerator

When the Chain module is used to compute WOTS chains, the IO requirements are still quite high: For each WOTS key generation, the 256 bit WOTS private key and a 256 bit starting address need to be transferred to the Chain module for l times, although their inputs only differ in a few bytes of the address, and l WOTS chain public keys each of 256 bit need to be transferred back.

To reduce this communication overhead, we implemented an XMSS-leaf accelerator module, replacing the software function treehash (see Figure 2). The Leaf module only requires a 256 bit address (leaf index), a 256 bit secret seed, and a 256 bit XMSS public seed as input. After the Leaf module finishes computation, the 256 bit L-tree root hash value is returned as the output.

Implementation. As shown in Figure 5, the Leaf module is built upon two sub-modules: a WOTS module and an L-tree module. The WOTS module uses the Chain module described in Section 5.3 to compute the WOTS chains and returns l 256 bit strings as the WOTS public key. Then, these l values are pairwise hashed together as described in Section 2.1 by the L-tree module. Finally, the output of the L-tree module (the root of the L-tree) is returned as the output of the Leaf module.

The WOTS module first computes the secret keys for each WOTS chain using a PRF\_priv module iteratively for l times. As opposed to the prf() computations during the WOTS chain, L-tree, and Merkle tree computations, the PRF\_priv module takes a private, not a public seed as input. For each iteration, the corresponding address is computed and sent to the PRF\_priv module as input as well. When the PRF\_priv module finishes, its output is written to a dual-port memory mem, which has depth l and width 256 bit. Once the secret keys for the l WOTS chains have been computed and written to mem, the WOTS public key computation begins. This is done by iteratively using the Chain module (see Section 5.3) for l times. The output of the Chain module is written back to mem, overwriting the previously stored data.

Once the WOTS public key computation finishes, the L-tree module begins its work. The building block of the L-tree module is a RAND\_HASH module which implements the tree-hash function as described in Section 2.1. It takes in a 256 bit XMSS public seed, two 256 bit data strings, and a 256 bit address string as input and returns a 256 bit output. Within the hardware module RAND\_HASH, three prf() and one h() computations are carried out in sequence using the modules PRF and H. The result generated by the first prf() computation is buffered as the 256 bit key while the results from the following prf() computations are buffered as

Fig. 5: Diagram of the Leaf accelerator wrapper including all the accelerator modules. (control logic is simplified). The SHA256XMSS module uses SHA256, the Chain module uses SHA256XMSS, and the Leaf module uses Chain and SHA256XMSS.

the two 256 bit masks. The two 256 bit input data strings then get each XOR-ed with a mask and sent to the final h() computation together with the previously computed key. The result of the h() computation is returned as the output of the RAND\_HASH module.

The L-tree module constructs the nodes on the first level by first reading out two adjacent leaf nodes from the dual-port memory mem by issuing two simultaneous read requests to adjacent memory addresses. The memory outputs are sent to the RAND\_HASH module as input data. Once RAND\_HASH finishes computation, the result is written back to mem in order (starting from memory address 0). Since the L-tree is not a complete binary hash tree, it occasionally happens that there is a last node on one level that does not have a sibling node. This node is read out from mem and immediately written back to the next available memory address. This pattern of computation is repeated until the root of the L-tree is reached. This root is returned as the output of the Leaf module.

In order to minimize the resource usage of the Leaf module, all the hash computations are done by interfacing with the same SHA256XMSS module. Figure 5 shows a diagram of the main building blocks of the Leaf module. The "precomputation" optimization for the prf() computations again can be enabled for the SHA256XMSS module before synthesis. When the Leaf module is added to the Murax SoC as a hardware accelerator, it also provides a Chain, a SHA256XMSS, and a SHA256 accelerator since these modules are all used as building blocks in the Leaf module.

| Design                       | Cycles     |                                             | Area (ALM) | Reg.                 | FMax<br>(MHz)       | Time (ms)           | Time×Area<br>(relative) | Speedup              |

|------------------------------|------------|---------------------------------------------|------------|----------------------|---------------------|---------------------|-------------------------|----------------------|

| Leaf<br>+ PRECOMP            | 447<br>306 | $\times 10^3$<br>$\times 10^3$              | 1000       | 6270<br>6840         | 86.1<br>92.8        | 5.20<br>3.30        | _                       | 1.00<br>1.58         |

| Murax<br>+ Leaf<br>+ PRECOMP | 450        | $7 \times 10^6$ $\times 10^3$ $\times 10^3$ | 6460       | 1660<br>9270<br>9540 | 152<br>86.6<br>93.1 | 182<br>5.19<br>3.32 |                         | 1.00<br>35.0<br>54.8 |

**Table 5:** Performance of the hardware module Leaf and performance comparisons of calling the treehash function from the RISC-V software on a Murax SoC and on a Murax SoC with a Leaf accelerator, with parameters n=32 and w=16.

Evaluation. Table 5 shows performance, resource requirements, and maximum frequency of the Leaf module. Enabling the "pre-computation" optimization ("+ PRECOMP") gives a 1.58× speedup at the cost of a small area overhead. Calling the accelerator in function treehash in the design "Murax + Leaf + PRECOMP" brings a 54.8× speedup over the pure software implementation on the plain Murax design. More importantly, as we can see from the Table (row "Leaf + PRECOMP" and "Murax + Leaf + PRECOMP"), the IO overhead is no longer impacting the performance of the hardware accelerator Leaf.

Table 6 shows the performance impact of the Leaf module on XMSS key generation, signing and verification (Murax compared with "Murax + Leaf" and "Murax + Leaf + PRECOMP"). When a Leaf module is added in the Murax SoC, it accelerates the functions treehash, gen\_chain, hash768 and hash1024 in XMSS. For the key-generation operation, the Leaf module accounts for a 54.1× speedup with "PRECOMP" enabled. The Leaf module is not used during verification and hence does not affect its execution time. The BDS algorithm [7] for signing does make use of the Leaf accelerator: For signing the first 16 XMSS leaves, on average a 42.8× speedup is achieved.

#### 6 Performance Evaluation

Table 6 shows performance, resource requirements, and maximum frequency of different designs for the XMSS operations: key generation, signing, and verification. Since the runtime of the BDS signature algorithm [7] varies depending on the leaf index, we report the average timing for the first 16 signature leaves of the XMSS tree. To accelerate the key generation, signing and verification operations in the XMSS scheme, our hardware accelerators ("SHA256", "SHA256XMSS", "Chain" and "Leaf") can be added to the Murax SoC, which leads to good speedups as shown in Table 6. In general, the more computations we delegate to hardware accelerators, the more speedup we can achieve in accelerating XMSS computations. However, at the same time, more overhead is introduced in the hardware resource usage, which is a trade-off users can choose depending on

| Design                                                 | Cycles         | Reg. | Area<br>(ALM) | BRAM (Blocks) | FMax<br>(MHz) | Time | е            | Time×<br>Area | Speedup |  |  |

|--------------------------------------------------------|----------------|------|---------------|---------------|---------------|------|--------------|---------------|---------|--|--|

| key generation                                         |                |      |               |               |               |      |              |               |         |  |  |

| Murax                                                  | 28,300,000,000 | 1660 | 1350          | 132           | 152           | 186  | s            | 11.2          | 1.00    |  |  |

| + SHA256                                               | 4,870,000,000  | 3880 | 2860          | 132           | 99.9          | 48.8 | $\mathbf{S}$ | 6.23          | 3.82    |  |  |

| + SHA256XMSS                                           | 3,810,000,000  | 4890 | 3490          | 132           | 97.8          | 39.0 | $\mathbf{s}$ | 6.09          | 4.78    |  |  |

| + PRECOMP                                              | 3,350,000,000  | 5170 | 3660          | 132           | 97.6          | 34.3 | $\mathbf{S}$ | 5.60          | 5.43    |  |  |

| + Chain                                                | 912,000,000    | 6220 | 4350          | 132           | 91.6          | 9.96 | $\mathbf{S}$ | 1.93          | 18.7    |  |  |

| + PRECOMP                                              | 742,000,000    | 6460 | 4560          | 132           | 95.2          | 7.80 | $\mathbf{S}$ | 1.59          | 23.9    |  |  |

| + Leaf                                                 | 466,000,000    | 9270 | 6460          | 145           | 86.6          | 5.38 | $\mathbf{S}$ | 1.55          | 34.6    |  |  |

| + PRECOMP                                              | 320,000,000    | 9540 | 6500          | 145           | 93.1          | 3.44 | S            | 1.00          | 54.1    |  |  |

| signing (average of the first 16 XMSS leaf signatures) |                |      |               |               |               |      |              |               |         |  |  |

| Murax                                                  | 64,800,000     | 1660 | 1350          | 132           | 152           | 426  | ms           | 8.85          | 1.00    |  |  |

| + SHA256                                               | 11,200,000     | 3880 | 2860          | 132           | 99.9          | 112  | ms           | 4.93          | 3.81    |  |  |

| + SHA256XMSS                                           | 8,750,000      | 4890 | 3490          | 132           | 97.8          | 89.5 | ms           | 4.83          | 4.76    |  |  |

| + PRECOMP                                              | 7,700,000      | 5170 | 3660          | 132           | 97.6          | 78.8 | ms           | 4.45          | 5.40    |  |  |

| + Chain                                                | 2,070,000      | 6220 | 4350          | 132           | 91.6          | 22.6 | ms           | 1.52          | 18.9    |  |  |

| + PRECOMP                                              | 1,700,000      | 6460 | 4560          | 132           | 95.2          | 17.8 | ms           | 1.26          | 23.9    |  |  |

| + Leaf                                                 | 1,250,000      | 9270 | 6460          | 145           | 86.6          | 14.4 | ms           | 1.44          | 29.5    |  |  |

| + PRECOMP                                              | 926,000        | 9540 | 6500          | 145           | 93.1          | 9.95 | ms           | 1.00          | 42.8    |  |  |

|                                                        |                |      | verifi        | cation        |               |      |              |               |         |  |  |

| Murax                                                  | 15,200,000     | 1660 | 1350          | 132           | 152           | 99.6 | ms           | 5.17          | 1.00    |  |  |

| + SHA256                                               | 2,610,000      | 3880 | 2860          | 132           | 99.9          | 26.1 | ms           | 2.88          | 3.81    |  |  |

| + SHA256XMSS                                           | 2,060,000      |      | 3490          | 132           | 97.8          | 21.1 | ms           | 2.84          | 4.73    |  |  |

| + PRECOMP                                              | 1,800,000      | 5170 | 3660          | 132           | 97.6          | 18.5 | ms           | 2.61          | 5.39    |  |  |

| + Chain                                                | 649,000        |      | 4350          | 132           | 91.6          | 7.08 | ms           | 1.19          | 14.1    |  |  |

| + PRECOMP                                              | 541,000        | 6460 | 4560          | 132           | 95.2          | 5.68 | ms           | 1.00          | 17.5    |  |  |

| + Leaf                                                 | 649,000        | 9270 | 6460          | 145           | 86.6          | 7.49 | ms           | 1.87          | 13.3    |  |  |

| + PRECOMP                                              | 541,000        | 9540 | 6500          | 145           | 93.1          | 5.80 | $_{ m ms}$   | 1.46          | 17.2    |  |  |

Table 6: Time and resource comparison for key generation, signing and verification on a Cyclone V FPGA (all values rounded to three significant figures with  $n=32,\,w=16$  and h=10). "Time" is computed as quotient of "Cycles" and "FMax"; "Time×Area" is computed based on "Area" and "Time" relative to the time-area product of the respective most efficient design (gray rows); "Speedup" is computed based on "Time" relative to the respective Murax design.

their needs. The best time-area product for the expensive key generation and the signing operations is achieved in design "Murax + Leaf" with "PRECOMP" enabled. For the less expensive verification operation, the "Murax + Chain + PRECOMP" design gives the best time-area product.

The maximum frequency for the designs is heavily impacted by our hardware accelerators (which is accounted for in our speedup and time-area product reports), dropping from  $152\,\mathrm{MHz}$  down to as low as  $86.6\,\mathrm{MHz}$ . If a high instruction throughput of the Murax SoC is required for an embedded application that is

using our XMSS accelerators, a clock-frequency bridge between the APB and our accelerators might be necessary to enable independent clocks; however, this does not have an impact on the wall-clock speedup of our accelerators.

For a tree height of h=10, i.e., a maximum number of  $2^h=1024$  signatures per key pair, the time for XMSS key generation can be as short as only 3.44s using our hardware accelerators. Even more signatures per key pair are conceivably possible using multi-tree XMSS, as shown in Table 7 (row "XMSS^MT<sup>b</sup>"). By use of our hardware accelerators, we expect a similar speedup in accelerating XMSS^MT as we achieved in XMSS. Signing and verification computations are very efficient on our hardware-software co-design for all the SHA-256 parameter sets, i.e.,  $n=32, w=16, h=\{10,16,20\}$ : For h=10, signing takes only 9.95 ms and verification takes only 5.80 ms. For a bigger tree height, e.g., h=20, signing and verification are only slightly more expensive: Signing takes 11.1 ms and verification takes 6.25 ms, as shown in Table 7 (row "XMSS° with (n,h,w)=(32,20,16)"). Our experiments show that running XMSS is very much feasible on a resource restricted embedded device such as the Murax SoC with the help of efficient dedicated hardware accelerators.

## 7 Related Work

We first compare our work with a very recent work [9] which shows a similar software-hardware co-design for XMSS. Then, we summarize all the existing FPGA-based implementations on other hash-based signature schemes. Finally, comparisons with implementations of XMSS on other platforms are provided. Detailed comparison results are shown in Table 7.

In 2019, Ghosh, Misoczki and Sastry [9] proposed a software-hardware codesign of XMSS based on a 32-bit Intel Quark microcontroller and a Stratix IV FPGA. WOTS computations are offloaded to a WOTS hardware engine which uses a general-purpose Keccak-400 hash core as building block. In their design, generating one WOTS key pair takes 355,925 cycles, consuming 2963 combinational logic cells and 2337 register cells. This hardware engine has the same functionality as our WOTS module described in Section 5.4. In our design, the WOTS module (with "+ PRECOMP") takes 279,388 cycles for generating a key pair. The synthesis result of our WOTS module on the same FPGA reports a usage of 2397 combinatorial logic cells and 3294 register cells. However, as shown in [9], keccak-400 has a 6× smaller Time×Area compared to SHA-256 when implemented on a 14nm technology. Given such big differences in the building hash core, a fair comparison between the two WOTS designs is not possible.

By use of the WOTS hardware engine, running the XMSS reference implementation on their software-hardware co-design with n=32, h=16, w=16 takes  $4.8\times 10^6$  cycles in verification on average (key generation and complete signature generation are not included in their tests). To achieve a better comparison, we run a full XMSS test with the same parameter set on the "Murax + Leaf + PRECOMP" design. As shown in Table 7, in terms of cycle count, our design achieves an over  $8.5\times$  bigger speedup compared to [9] in accelerating the verifi-

| Design                             | Parameters $(n, h, w)$ | Hash       | Feature                | Platform          |      | KeyGen.<br>×10 <sup>9</sup> cyc. | $\begin{array}{c} {\rm Sign} \\ \times 10^6 {\rm cyc.} \end{array}$ | Verify $\times 10^6$ cyc. |

|------------------------------------|------------------------|------------|------------------------|-------------------|------|----------------------------------|---------------------------------------------------------------------|---------------------------|

| CMSS [26]                          | 32,(10x3),8            | SHA-512    | $_{ m HW}$             | Virtex-5          | 170  | 1.2                              | 3.7                                                                 | 2.2                       |

| SPHINCS [1]                        | _                      | ChaCha-12  | $_{\mathrm{HW}}$       | Kintex-7          | 525  | _                                | 0.80                                                                | 0.035                     |

| XMSS [14]                          | $16,\!10,\!16$         | AES-128    | AES                    | SLE78             | 33   | 0.62                             | 3.3                                                                 | 0.56                      |

| $\overline{\mathrm{XMSS}^b}$       | 32,10,16               | SHA-256    | SW                     | Intel i5          | 3200 | 5.6                              | 13                                                                  | 3.0                       |

| $\mathbf{XMSS}^o$                  | $32,\!10,\!16$         | SHA-256    | SW-HW                  | Murax SoC         | 93   | 0.32                             | 0.93                                                                | 0.54                      |

| $\overline{\mathrm{XMSS}^b}$       | 32,16,16               | SHA-256    | SW                     | Intel i5          | 3200 | 360                              | 14                                                                  | 3.1                       |